# E21: Digital System Design Lectures, Fall 2000

Dr. Bruce A. Maxwell, Asst. Professor Department of Engineering Swarthmore College

### **Course Description**

This course covers digital system design. Topics include Boolean logic, digital representations, and techniques for design of combinational, sequential, and asynchronous circuits. We also study I/O interfaces, communication protocols, and micro-controller architecture. Labs focus on CAD techniques, VHDL [Very high speed integrated circuit Hardware Description Language], and programmable logic devices.

Prerequisites: CS21, E11, or permission of instructor

#### © 2000 Bruce A. Maxwell

This material is copyrighted. Individuals are free to use this material for their own educational, non-commercial purposes. Distribution or copying of this material for commercial or for-profit purposes without the prior written consent of the copyright owner is a violation of copyright and subject to fines and penalties.

# Introduction

Why digital logic?

- Reproducibility of results

- If you have the same inputs, a well-designed circuit gives you the same outputs

- Ease of design

- You don't have to use calculus to model a digital circuit at the functional level

- Small digital circuits can be visualized mentally without difficulty

- Flexibility and functionality

- Try building a hard-to-break easy-to-use encryption algorithm using analog components

- Programmability

- Digital circuits, if properly designed, can be programmed to do different things

- Economy

- Digital circuits are cheap and small

- Advancing technology

- Digital technology continues to improve: faster, cheaper, smaller, easier to use

# Administrivia

## The most important thing...

http://www.palantir.swarthmore.edu/~maxwell/classes/e21

- homeworks

- readings

- syllabus

- labs

- other course links

- VHDL sites, hardware sites, tutorial sites, etc..

## Focus of the course

- Basics of digital logic (pretty simple)

- Programmable digital devices: flexible design

- Trouble-shooting digital circuits

- Sensors and how to integrate them into digital systems

- Microcontrollers and FPGAs as the "brains" of small (embedded) digital systems

- By the end you should have the knowledge necessary to begin designing computer peripherals and stand-alone digital devices.

# **Final project**

- The last 4-5 weeks you will be doing your own final project, start thinking about it now

- Past years:

- keyed security system, and it worked

- evolvable hardware project

- parallel port communication & control of external devices

- lap counter

- This year:

- Security system for your room

- Interface with a computer

- Your own LED programmable scoreboard

- Additional smart sensors for a robot

- ASIC for solving a particular problem (like finding lots of primes, quickly)

- Anything else you can dream up...

#### **Expectactions**

- Keep up: we will move quickly through much of the introductory digital logic topics

- Let me know if we're moving too quickly or too slowly

- Lab work is very important, because you won't learn about digital design unless you do it

- Digital design is 10% fun (at best) and 90% turn the crank

- We will be using good tools to make turning the crank faster & easier

#### **Syllabus**

- Textbook: only one required, I suggest getting a separate VHDL text

- Problem sets: Handed out Monday of each week, due the following Monday, in class.

- Labs: you can work in pairs.

- Labs: will occur approximately every 2 weeks

- Final project: labs will lead into the project, for which you will have the last 4-5 weeks

- Lab Notebooks (strongly recommended): each of you will need to keep a lab notebook (to be handed in with each lab). In this notebook you need to keep enough information for someone else to recreate your work. You should also sign and date each entry as you complete it. Some of your work could potentially lead to a patent.

- Late policy

## The basis of digital systems

#### $1^{\prime}s$ and $0^{\prime}s$

- Using electricity we can represent logical values as voltages

- Hi range v. Lo range with a section in the middle (unspecified value)

- Different hardware families have different ranges

- As long as we can guarantee the specs, a digital system will reproduce a signal given the same set of inputs.

#### Logic gates

Electrical implementations of truth tables

- AND, OR, NOT (and symbols)

- NAND

- NOR

- XOR, Buffer, Multiple input AND, OR, NAND, and NOR functions

| Input A | Input B | AND | OR | NAND | NOR | XOR |

|---------|---------|-----|----|------|-----|-----|

| 0       | 0       | 0   | 0  | 1    | 1   | 0   |

| 0       | 1       | 0   | 1  | 1    | 0   | 1   |

| 1       | 0       | 0   | 1  | 1    | 0   | 1   |

| 1       | 1       | 1   | 1  | 0    | 0   | 0   |

### **Table 1: Truth Tables**

Example question: So if I wanted to add two 1-bit numbers, what would be appropriate logic gates to generate their sum and carry? [sum = XOR, carry = AND]

### **SSI** components

Small-Scale Integration components were the first building blocks.

- Usually use 20 gates or less

- Usually cost around 25 cents

- 7400 series (letters tell you the family, numbers the configuration & function)

- 7400 is a quad 2-input NAND gate

- 7404 is a hex inverter

- 7432 is a quad 2-input OR gate (and so on)

SSI components are usualy used to interface with other, more complex components. It's not efficient to use them as the base building blocks except in some prototypes.

Note: mainframes and supercomputers used to be built out of SSI components. Cray designed the Cray-1 from PCBs with nothing but NAND gates on them because they were fast.

# The basis of digital systems

### **Number Systems**

- Living with 1's and 0's is fine if you can use them to represent something.

- Binary is a number system (base 2)

- Each position in a binary system is a power of 2 (starting with  $2^0$  on the right)

- Conversion from decimal to binary: keep dividing by 2, put the remainders right to left

Example: 26 -> binary = 11010

- Conversion from binary to decimal: sum up the value of each place containing a one

- Example 101010 = 2 + 8 + 32 = 42

- Using binary numbers can be a real pain, and they are difficult to read.

- Octal and Hexadecimal are two number systems that make it easier to read "bits"

- Octal is base 8, and 3 bits (binary numbers) make one octal number.

- Hexadecimal is base 16, and 4 bits make one hexadecimal number

- Hexadecimal is preferred, we think in terms of bytes (8 bits) not 3, 6, or 9 bit values

- Hexadecimal values are (0-9, A-F)

- Convert 61453 (decimal) to hex -> F00D

- 61453 / 2 = 30726 (1)

- 30726 / 2 = 15363 (01)

- 15363 / 2 = 7681 (101)

- 7681 / 2 = 3840 (1101)

- 3840 / 2 = 1920 (0 1101)

- $1920 / 2 = 960 (00 \ 1101)$

- $960/2 = 480 \ (000 \ 1101)$

- $480/2 = 240 (0000 \ 1101)$

- $240/2 = 120(0\ 0000\ 1101)$

- $120/2 = 60(00\ 0000\ 1101)$

- $60/2 = 30 (000\ 0000\ 1101)$

- $30/2 = 15(0000\ 0000\ 1101)$

- $15/2 = 7 (1\ 0000\ 0000\ 1101)$

- $7/2 = 3 (11\ 0000\ 0000\ 1101)$

- 3/2 = 1 (111 0000 0000 1101)

- 1 / 2 = 0 (1111 0000 0000 1101) = (F 0 0 D)

### So how do we represent negative numbers?

- Use a sign bit

- makes adding and subtracting a pain

- two representations of zero

- Use two's-complement representation (add binary value of low n-1 bits to  $-(2^{n-1})$ )

- Think about it as a wheel

- Like signed binary, the high bit indicates the sign of the number

- sign extension: pad the high bits with whatever was in the old high bit

- To invert In binary, complement each digit and then add 1

- Range: one more negative digit than positive:  $-r^n$  to  $(r^n 1)$

- adding two's complement

- add them just like two binary numbers, just ignore any carry out of the high bit

- overflow rule: when the two numbers have the same sign and the sign changes

- subtraction: invert one number and add them

- Examples: -4 + 4, 5 + 6, -7 + 5, 9 + 9

#### Other representations...

- Binary Coded Decimals

- 0-9 using 4 bits

- low 4 bits of the ASCII representation are BCD

- useful for representing money transactions

- Packed BCD representation

- use a fixed number of 4-byte chunks with one chunk being the sign

- sign chunk is usually all 1's

- Gray codes: used for encoding position: only one bit changes at a time

- Gray codes are used in altimeters, motor encoders, etc.. (why?)

- ASCII codes: used for encoding both actions and characters

- Encoding actions: traffic light example:

- NS go, NS wait, NS delay, EW go, EW wait, EW delay, G/Y/R for each,

- 6 codes: how many bits?

- Often choose an encoding that minimizes the number of gates needed

- balance experimentation with time

#### **Error-detection and error correction**

Error detection: use a dictionary of code words that is a subset of the 2<sup>n</sup> possible code words

• A failure occurs when an invalid code word is sent

Say we want to know all cases where a single bit might be flipped

- Think about a hypercube, where each node represents a bit string

- Each node only takes a one bit modification to get to its neighbor

- Distance is defined as how many steps you have to take to get between two nodes

If we want to know when any single bit is flipped, which nodes on the hypercube can we use?

- Any set of nodes such that no two valid code words are less than a distance 2 apart

- using a parity bit (either even or odd parity) allows such a code

Now say we want to know how to correct one-bit errors and detect 2-bit errors

- Create a code with a minimum distance of 3

- A one bit error will cause an invalide code word, but it will be closest to one valid code

- A two bit error will be detectable, but not repairable

- Need to use more bits if you want to detect and correct 2 bit errors

- In general, use 2c + 1 bits to correct up to c bit errors.

### Hamming Codes

- A general method for constructing error correcting codes of minimum distance 3

- There are i check bits for  $2^{i}$ -1-i information bits

- The bits in positions that are powers of 2 are the check bits (1, 2, 4, ...)

- The check bits deal only with the bits in those positions that have a 1 in the same bit when their position is expressed in binary: for a 7-bit code: 1 -> 3, 5, 7, 2->3, 6, 7; 4->5, 6, 7

- The check bits will have even parity for their group

- There are at least two parity bits for any information bit

- To correct a bit, we locate the column that possesses all of the odd parity groups

## Example:

1-information bit => 2 code bits

- Possible data values are 0/1

- Code bits must make even parity, so 000 / 111 are the legal codes

- A single bit flip can be corrected

# **Designing Simple Logic Circuits**

## **Combinational Logic**

- Circuit output is a function only of the current inputs.

- Inputs: signals, or variables

- Circuit: expressions, which are variables related by Boolean expressions

- Boolean logic is defined by a set of axioms

- Boolean logic: two-value logic (X = 0 iff X != 1)

- Boolean product: AND function (1\*X = X, 0\*X = 0)

- Boolean sum: OR function (1 + X = 1, 0 + X = X)

- Boolean inverse: 1 -> 0, 0 -> 1

- Boolean theorems

- Sum axioms

- X + 0 = X

- X + 1 = 1

- X + X = X

- X + X' = 1)

- Product axioms

- X\*1 = X

- X\*0 = 0

- X\*X = X

- X \* X' = 0

- DeMorgan's theorem s

- (X1 \* X2 \* ... \* Xn)' = X1' + X2' + .... + Xn'

- (X1 + X2 + ... + Xn)' = X1' \* X2' \* .... \* Xn'

### **Standard Representations**

SOP representation: all of the 1 combinations

POS representation: all of the 0 combinations, but invert variables and use product of sums

Example: F = Sum(1, 2, 4, 6, 7)

- SOP =  $\overline{A} \overline{B} C + \overline{A} B \overline{C} + A \overline{B} \overline{C} + A B \overline{C} + A B C$

- POS =  $(A+B+C)(A+\overline{B}+\overline{C})(\overline{A}+B+\overline{C})$

Question: can we do it better?

Minimization using Boolean logic...

• SOP expression: Combine the last two terms into AB, combine 2nd and 4th to get  $\overline{BC}$ , combine 4th and 5th term to get  $\overline{AC}$ .

Have everyone do F = Sum(0, 2, 6, 7)

### Is there a better way?

Group minterms together that share bits

Do it graphically: Karnaugh maps

- 3 and 4 variable K-maps

- 5 and 6 variable K-maps (Bill's method)

- Group the 1's

# **Designing Simple Logic Circuitsi**

### More on Karnaugh Maps

- When you design a circuit, you don't always care about every input all the time

- Priority situation: Allows you to collapse the truth table to just a few lines

- Example: Bev, Pop, 1, 2 case

- Drawing the Karnaugh map becomes easy

- Sometimes you don't care about the outputs

- You usually care with combinational circuits, but not necessarily with sequential ones

- Example: case where you only care about 5 of the 8 cases (last three will never occur)

- You can label a don't care as either a 1 or a 0 on the Karnaugh map

- You can use it in a group as you see fit to minimize the expression

- Static Hazards

- Can occur when you go between disconnected groups in a K-map

- One solution is to have overlapping groups (more terms than you really need)

- Other solution is to use sequential logic that only samples during stable periods

### Procedure for designing a combinational circuit of 6 variables or less

- Write the truth table

- Fill a Karnaugh-map for each output variable

- Group the 1s by powers of 2

- Express each group as a term in the Boolean expression

- Write the Boolean expression

- Draw the logic diagram

- Build the circuit

# When Karnaugh Maps don't work...

- Karnaugh maps are good up to 6 variables

- Difficult to visualize hypercubes beyond 6 dimensions

## **Quine-McCluskey Method**

Tabular method works for 6-10 variables, maybe a few more

- 1. Find all of the size 1-subcubes (minterms in the truth table)

- 2. n = 1

- 3. Group the minterms according to how many 1's they have in them

- 4. Use terms in adjacent groups to form (n+1)-subcubes

- 5. Label the level n minterms as to whether they are covered by a level n+1 subcube

- 6. Increment n and loop back to step 3

The list of terms not covered by a subcube at a higher level are the list of Prime Implicants

- Example 1: F = Sum(2, 3, 5, 6, 7)]

- Follow the procedure to create groupings at the highest level possible

- Each non-covered term is a prime implicant

- Create a second table with the prime implicants

- Pick the terms you need from the table (minimal cover generation)

| Group ID | Subcube<br>Minterms        | Subcube<br>Value  | Subcube<br>Covered |

|----------|----------------------------|-------------------|--------------------|

| G1       | (2)                        | 010               | yes                |

| G2       | (3, 5, 6)                  | 011<br>101<br>110 | yes<br>yes<br>yes  |

| G3       | (7)                        | 111               | yes                |

| G1       | (2, 3)<br>(2, 6)           | 01X<br>X10        | yes<br>yes         |

| G2       | (3, 7)<br>(5, 7)<br>(6, 7) | X11<br>1X1<br>11X | yes<br>no<br>yes   |

| G1       | (2, 3, 6, 7)               | X1X               | no                 |

| Prime<br>Implicant | Expression | Minterms | 2 | 3 | 5 | 6 | 7 |

|--------------------|------------|----------|---|---|---|---|---|

| P1                 | AC         | (5, 7)   |   |   | X |   | Х |

| P2                 | Р2 В       |          | X | X |   | X | Х |

### **Minimal Cover Generation**

The complete list of Prime Implicants [PI] do not necessarily form the minimal cover expression.

- 1. Find the Essential Prime Implicants [EPI]

- Essential prime implicants cover a minterm not covered by any other PI

- Make a table with a row for each PI and a column for each minterms

- Mark the minterms covered by each PI

- Any column with only one mark identifies an EPI, which must be included in the function

- 2. Find the Minimal Cover Expression

- Intelligently select from the remaining PIs to get a minimal cover expression

- Method 1:

- Form a POS, where each sum is the set of PIs that cover a particular minterm

- Multiply it out to get a SOP term

- Remove any expressions from the SOP that are covered by simpler expressions

- The remaining terms are the possible choices to combine with the EPIs

- Method 2:

- Depth-first search, and compare the resulting possibilities

# **Designing Simple Logic Circuits**

### Minimal Cover Generation with Quine-McClusky

- 1. Find the Essential Prime Implicants [EPI]

- Any column with only one mark identifies an EPI, which must be included in the function

- 2. Find the Minimal Cover Expression

- Intelligently select from the remaining PIs to get a minimal cover expression

- Method 1:

- Form a POS, where each sum is the set of PIs that cover a particular minterm

- Multiply it out to get a SOP term

- Remove any expressions from the SOP that are covered by simpler expressions

- The remaining terms are the possible choices to combine with the EPIs

- Method 2:

- Depth-first search, and compare the resulting possibilities

- Example 2: random function [minterms 0, 2, 4, 3, 6, 9, 7, 11, 13, 15]

| Group ID | Subcube<br>Minterms | Subcube<br>Value | Subcube<br>Covered? |

|----------|---------------------|------------------|---------------------|

| GO       | (0)                 | 000              | yes                 |

| G1       | (2)                 | 0010             | yes                 |

|          | (4)                 | 0100             | yes                 |

| G2       | (3)                 | 0011             | yes                 |

|          | (6)                 | 0110             | yes                 |

|          | (9)                 | 1001             | yes                 |

| G3       | (7)                 | 0111             | yes                 |

|          | (11)                | 1011             | yes                 |

|          | (13)                | 1101             | yes                 |

| G4       | (15)                | 1111             | yes                 |

| G0       | (0, 2)              | 00X0             | yes                 |

|          | (0, 4)              | 0X00             | yes                 |

| G1       | (2, 3)              | 001X             | yes                 |

|          | (2, 6)              | 0X10             | yes                 |

|          | (4, 6)              | 01X0             | yes                 |

| G2       | (3, 7)              | 0X11             | yes                 |

|          | (3, 11)             | X011             | yes                 |

|          | (6, 7)              | 011X             | yes                 |

|          | (9, 11)             | 10X1             | yes                 |

|          | (9, 13)             | 1X01             | yes                 |

| G3       | (7, 15)             | X111             | yes                 |

|          | (11, 15)            | 1X11             | yes                 |

|          | (13, 15)            | 11X1             | yes                 |

| Group ID | Subcube<br>Minterms | Subcube<br>Value | Subcube<br>Covered? |

|----------|---------------------|------------------|---------------------|

| G0       | (0, 2, 4, 6)        | 0XX0             | no                  |

| G1       | (2, 3, 6, 7)        | 0X1X             | no                  |

| G2       | (3, 7, 11, 15)      | XX11             | no                  |

|          |                     | 1XX1             | no                  |

| Prime | Expression                 | Minterms     | 0 | 2 | 3 | 4 | 6 | 7 | 9 | 11 | 13 | 15 |

|-------|----------------------------|--------------|---|---|---|---|---|---|---|----|----|----|

| P1    | $\overline{A}\overline{D}$ | (0, 2, 4, 6) | X | X |   | X | X |   |   |    |    |    |

| P2    | ĀC                         | (2, 3, 6, 7) |   | X | X |   | X | X |   |    |    |    |

| P3    | CD                         | (3,7,11,15)  |   |   | X |   |   | X |   | X  |    | X  |

| P4    | AD                         | (9,11,13,15) |   |   |   |   |   |   | X | X  | X  | X  |

- P1 and P4 have to be in the expression (essential prime implicants)

- Shaded columns are the only ones not covered by P1 or P4

- Can pick either P2 or P3 to complete the expression

### **Example of SOP method**

Consider the function: F = Sum(2, 6, 7, 8, 9, 13, 15)

• Prime implicants are:  $\overline{A} C \overline{D}$ ,  $\overline{B} \overline{C} D$ ,  $\overline{A} B C$ ,  $A\overline{B}D$ , BCD,  $ACD^{\overline{}}$

| Prime | Expression                    | Minterms | 2 | 6 | 7 | 8 | 9 | 13 | 15 |

|-------|-------------------------------|----------|---|---|---|---|---|----|----|

| P1    | Ā C D                         | (2, 6)   | X | Х |   |   |   |    |    |

| P2    | $\overline{B} \overline{C} D$ | (8, 9)   |   |   |   | X | X |    |    |

| P3    | Ā B C                         | (6, 7)   |   | X | X |   |   |    |    |

| P4    | ABD                           | (9, 13)  |   |   |   |   | X | X  |    |

| P5    | BCD                           | (7, 15)  |   |   | X |   |   |    | Х  |

| P6    | ACD                           | (13, 15) |   |   |   |   |   | X  | Х  |

- Build the POS expression for each column not covered by an EPI (shaded columns)

- F = (P3 + P5)(P4 + P6)(P5 + P6)

- F = (P3 + P5)(P4P5 + P5P6 + P4P6 + P6): P6 covers P5P6 and P4P6

- F = (P3 + P5)(P4P5 + P6)

- F = P3P4P5 + P3P6 + P4P5 + P5P6: P4P5 covers P3P4P5

- F = P3P6 + P4P5 + P5P6

- Choose any of these three combinations to minimally cover the circuit

### **Technology Mapping**

- Converting AND-OR gates to NAND/NOR gates

- Rule 1: xy = ((xy)')': AND gate is a NAND gate with an inverter on the output

- Rule 2: x+y = ((x + y)')' = (x'y')': OR gate is a NAND gate with inverters on the inputs

- Rule 3: xy = ((xy)')' = (x' + y')': AND gate is a NOR gate with inverters on the inputs

- Rule 4: x+y = ((x + y)')': OR gate is a NOR gate with an inverter on the output

- Example: ab + b'c + a'c

- convert to NAND gates

- convert to NOR gates

- After conversion, optimize by removing inverter pairs

- Example: full-adder function (sum)

- F = x'yc' + xy'c' + x'y'c + xyc

### **Term Decomposition**

- Sometimes we need to use gates with fewer inputs

- programmable logic often requires a fixed number of gate inputs

- Term decomposition turns m-input gates into 2 or more n-input gates where n < m.

- Term decomposition must occur before technology mapping

- Process

- Make a table with the levels, number of inputs, and number of gates

- Each level takes an integral number of gates (inputs / inputs per gate)

- Remaining inputs go to the next level

- There will be log\_m(n) levels

- There may be numerous possible decompositions, you want to optimize it

- Example: Convert a 13 input AND gate to 2-input AND gates

| Level | Inputs | #gates |

|-------|--------|--------|

| 1     | 13     | 6      |

| 2     | 7      | 3      |

| 3     | 4      | 2      |

| 4     | 2      | 1      |

- Timing optimization

- There are often multiple different decompositions you can design

- Pick the one that optimizes timing

- minimize the longest path through the circuit

- Pick the one that reduces the difference between the shortest and longest paths

- minimizes the likelihood of hazards

# **Logic Families**

## History

- 1930's: Relays

- 1940's: Vacuum tubes (350 volts = high) (MOSFETs developed)

- 1950's: Bipolar junction transistors

- 1960's: Integrated circuits, introduction of logic families, TTL, MOSFETs become practical

- 1970's: Development of the single-chip microprocessor

- 1980's: CMOS development, CMOS replaces TTL logic

- 1990's: 1-10 million transistor ICs

- 2000's: 100-200 million transistor ICs

# The Basic Inverter

•

To create an inverter you need a switch (any switch will do)

- The incoming signal controls the switch

- The outgoing signal is determined by how the switch is connected

- Pull-up network: circuit is usually low, closing the switch pulls the output high

- Pull-down network: circuit is usually high, closing the switch pulls the output low

Better inverters are faster because they pull the circuit high or low more quickly

Better inverters use less power because they have higher resistance to the disconnected voltage

The ideal inverter would have an instantaneous switch on boths sides:

- low source resistance to the connected power level

- high resistance to the disconnected power level

# **Bipolar Logic**

Basis of bipolar logic is the bipolar junction transistor.

- Diode: pn junction

- A positive voltage drop across a pn junction allows current to flow

- A negative voltage drop blocks current

- A large negative voltage drop lets lots of current flow

- Transistor: npn or pnp junction

- A positive voltage across the base-emitter pn junction allows current to flow

- It also allows current to flow across the np junction from the collector to the base

- The emitter output current is the sum of the base and collector input currents

- The collector current is a multiple of the base current up to a saturation point

Low input voltage for TTL is 0-0.8V, high input voltage is 2.0-5.0V, 0.8-2.0 is undefined

R V<sub>cc</sub> V<sub>out</sub> Gnd Common-emitter configuration

- Confguration

- Resistor on the base input

- Resistor on the collector input

- Emitter connected to ground

- Effect

- A positive input voltage on the base causes current to flow

- A zero voltage on the base causes little or no current to flow

#### A basic inverter

• The simplest case is a single transistor with two resistors (base and collector)

### **Basic AND and OR gates**

- OR gate: put two transistors in parallel to ground with each input connected to one transistor

- AND gate: put two tarnsistors in series to ground with each input connected to one transistor

### **TTL Families**

- 74 = Basic family

- 74H = High-speed TTL

- Uses smaller resistors for high switching speeds

- 74L = Low-power TTL

- Uses larger resistors for lower power dissapation

- 74S = Schottky

- Uses Schottky transistors that don't saturate (diode connecting the base and collector)

- 3ns / 19mW

- 74LS = Low-power Schottky

- Same switching speed than 74H, but higher resistances and 1/5th the power consumption

- 9ns / 2mW

- 74AS = Advanced Schottky

- Twice the switching speed of S, with the same power consumption

- 1.7ns / 8mW

- 74ALS = Advanced Low-power Schottky

- Faster than LS, with lower power consumption

- 4ns, 1.2mW

### CMOS: Complementary metal oxide semiconductor

- CMOS logic levels: traditionally 0-1.5V = low, 3.5-5V = high, 1.5-3.5 = undefined

- Other power levels are used as well: 3.3V, 2.7V, or lower for large ICs

- Typical static power dissapation for an SSI gate is 0.0125mW (12.5 uW)

- Typical dynamic power dissapation is 0.4mW/MHz (4mW at 10MHz)

- Power consumption is dependent upon voltage and frequency  $P = C_{PD}V_{CC}^2 f$

- $C_{PD}$  = Power dissapation capacitance, a characteristic of the transistors

- V = Power supply voltage, f = switching frequency

- Typical delays for an SSI gate are 5-10ns

- A MOSFET can be viewed as a voltage controlled resistor

- For a NMOS transistor, current flows from the drain to the source when the gate voltage is higher than the source.

- For a PMOS transistor, current flows from the source to the drain when the gate voltage is less than the source.

- In both cases, when there is current flowing, the MOS can be viewed as a resistor with a small resistance (10-100 ohms)

- When no current is flowing, the transistor appears as a large resistor (1 Mohm or more)

- Regardless of the voltage, very little current flows through the gate

### A basic inverter

- NMOS and PMOS are used in a complementary fashion to design CMOS

- Put a PMOS and an NMOS transistor in series

- Connect the PMOS to Vcc and the NMOS to ground

- Connect the input to the gates of both transistors

- When the input is high, the N-channel transistor is open, pulling the output to ground

- When the input is low, the P-channel transistor is open, pulling the output to Vcc

- When the input switches, there is a transistion period where current flows from Vcc to Gnd

- If the output is connected to another CMOS gate, then almost no power is used except when the input switches

- There is a capacitance at the gate that must be filled up/drained in order for the gate to reach steady-state

- This capacitance draws power

- This capacitance slows down the reaction time of the circuit

# **Logic Families**

## CMOS NAND and NOR gates

- k-input NAND and NOR gates can be created with CMOS logic

- For k-inputs there are k p-channel and k n-channel transistors

- For a NAND gate

- connect the p-channel transistors in parallel to Vcc

- connect the n-channel transistors in series between the p-channel transistors and ground

- connect each input to the gate of one p-channel and one n-channel transistor

- If any of the gates are low, the output is pulled to Vcc

- If all of the gates are high, the output is pulled to ground

- For a NOR gate

- connect the n-channel transistors in parallel to ground

- connect the p-channel transistors in series between the n-channel transistors and Vcc

- connect each input to the gate of one p-channel and one n-channel transistor

- If any of the gates are high, the output is pulled to ground

- If all of the gates are low, the output is pulled to Vcc

### Fanin

How many inputs can you have?

- Each transistor has a certain resistance

- Having more inputs means a higher resistance for the current to go through

- Each transistor has a certain capacitance

- Having more inputs means a higher capacitive load

Typically you don't want to have more than 4 (NOR) to 6 (NAND) inputs on a single gate

(NMOS have a lower resistance than PMOS, hence the difference)

If you want more than that, use cascaded gates

## Noninverting gates

You get inverting gates "for free" with CMOS technology (with most, in fact)

- AND

- Connect an inverter on the end of a NAND gate

- OR

- Connect an inverter on the end of a NOR gate

## Fanout

How many gates can you connect to the output of a CMOS circuit?

• Estimate: maximum LOW-state output current = 20uA, max input current = +/- 1uA

How much current are you going to draw from the circuit?

• Look at an inverter and treat the NMOS and PMOS transistors as appropriate resistances

- Model the load as a resistive load

- Thevinin equivalent of a 2k/1k voltage divider is a 667 ohm resistor and a 3.3 V source

- Case one (PMOS off, NMOS = 100 ohms): low output, .43 V (sinking current)

- Case two (PMOS = 100 ohms, NMOS off): high output, 4.78 V (sourcing current)

- Note: non-ideal inputs can cause problems because the transistor resistances change

- Manufacturer will usually specify a load current that indicates what the maximum loads can be in order to maintain voltages that are less than (greater than) Volmax (Vohmin)

- Typical fanout from a CMOS device to other CMOS devices is about 20

- Note: at switching speeds, we also have to worry about AC characteristics

- Capacitances slow down the switching speed

- More fanout, means a single source is driving more capacitances in parallel

### **CMOS Inputs**

CMOS inputs should always be connected

- Gate will generally show a "low" value

- Only small amounts of current (static) will switch the value

- Tie inputs to ground or a voltage source

- AND/NAND gates: tie the free input high

- OR/NOR gates: tie the free input low

### **Schmitt-Trigger Inputs**

- Because of feedback in the transistor, it follows a hysteresis curve

- If the input is a low value, then it won't go low again until the voltage rises above 2.9V

- If the input is a high value, then it won't go high again until the voltage drops below 2.1V

- The hysteresis helps to convert a noisy signal into a clean signal

## **Three-state Outputs**

- Sometimes you want a circuit to have no output

- When you have multiple circuits connected to a single wire, like a bus

- A three-state output has three states: high, low, and high-impedence

- You can think of this state as occurring when both the P- and NMOS transistors are off

- A three-state buffer takes as input the signal and an enable input

- when the enable is high, the output has the same value as the signal

- when the enable is low, both transistors are in the off state

- Connect a NAND gate to the PMOS gate, with EN and A as inputs

- Connect a NOR gate to the NMOS gate, with A and  $\overline{EN}$  as inputs

## **CMOS** families

Format: 74FFnn (54FFnn series are military grade)

- HC = High-speed CMOS

- HCT = High-speed CMOS, TTL compatible

- Input ranges are compatible with TTL input logic levels

- AC = Advanced CMOS (introduced in the mid 80's)

- Can sink lots of current in both directions

- Have extremely fast rise and fall times

- Are so fast in their rise and fall times that they can be a major source of analog noise

- ACT = Advanced CMOS, TTL compatible

- FCT = Fast CMOS, TTL compatible

- Faster switching times

- Lower power consumption

## **ECL: Emitter Coupled Logic**

Emitter coupled logic has always been the fastest logic available

- Take two bipolar transistors and connect their emitters

- Put the inputs to the transitor bases

- Each collector has its own resistor to a source voltage

- Basically a differential amplifier circuit

Emitter coupled logic works by changing currents

- The voltage change is very small (0.8V difference between high and low)

- They switch between two current flow states, off and on

- By switching the current, they switch the voltage through the collector resistors

Typical logic values are: 4.2 (low) and 5.0 (high)

ECL logic has always been the fastest available

- Current ECL family (ECLinPS) offers maximum delays under 0.5ns, including the signal delay getting on and off the chip (2GHz)

- Useful for communications gear, fiber-optic interfaces, and gigabit ethernet

ECL uses a lot of power

- Current is always flowing

- 26mW per gate, plus from 10-150mW per gate for termination

### VHDL: VHSIC Hardware Description Language

Digital Design (Old style)

- Using hierarchical methods, develop a design on paper

- [Post 1980: graphically design the circuit in CAD, or textually describe the structure

- Run the design through a discrete-event simulator]

- Build the circuit

- Test & debug cycle

How would you like to do digital design?

- Design in terms of circuit behavior and/or dataflow

- Use hierarchical methods

- Be able to describe and simulate the circuit at different levels

- Have designs be portable and reusable (modular)

Why do you want a hardware description language?

- To simulate hardware before implementing it

- To make design entry simpler than moving boxes and connecting wires

- To simplify verification and testing

- To simplify communication between different tools in a CAD environment

- To permit a standard for specification of inputs, outputs, and behavior of digital circuits

VHDL offers a standard language (IEEE Standard 1076 plus some additional standards)

- There are competitors (AHDL, Verilog HDL)

- Latest VHDL standard is 1993

- IEEE Standard 1164 standardizes data types for simulation

- IEEE Standard 1076.3 standardizes data types as they relate to hardware

How do you use VHDL?

- Design specification stage

- can describe subcomponents in VHDL using input/output specifications

- Design synthesis

- following certain styles of VHDL, you can map VHDL onto hardware

- Design simulation

- you can simulate your design before putting it into hardware

- Design documentation

- since VHDL is a standard, you can use the VHDL code as a formal specification

- provides an alternative to schematics

- provides an alternative to proprietary languages (Altera's AHDL is one example)

What is the overall structure of a hardware description language?

- At its essence, the HDL consists of methods of describing the two parts of a circuit

- The input/output characteristics of the circuit (entities)

- The internal functioning of the circuit (architectures)

- The other main structures of the language are designed to allow hierachical design

#### Simple Example 1: A comparator

#### **Entities & Architectures**

- The entity describes the input/output behavior of the circuit

- bit is a data type that describes a single wire carrying a Boolean value

- bit\_vector is a data type that describes a set of wires carrying Boolean values

- The architecture describes the function of the circuit

- When the bits on the A and B wire sets are identical, then the circuit outputs a '1'

- Otherwise, it outputs a '0'

- The conditional assignment statement is a basic tool of VHDL

- Note the architecture has to have a unique name, since there can be more than on architecture for a given entity

- A complete VHDL design must contain at least one entity and at least one architecture for that entity.

#### Other major language elements

- Packages

- Like the class declaration for a C++ class

- Specify constants, data types, function prototypes, aliases, etc..

- Tell the rest of the world how to use the functions declared in the related package body

- Package Body

- A set of functions/routines/circuits you can put into a library for reuse

- Configurations

- Specify which architectures go with which entities, etc.

#### Levels of Abstraction (styles)

- Behavioral

- Performance descriptions

- Test Benches

- Sequential Descriptions

- State machines

You can imply registers and register transfers using behavioral language, but there is no guarantee the circuit will work exactly as you want it to. Altera can handle some behavioral constructs

- Dataflow (Register-Transfer Level)

- State machines

- Register transfers

- Selected assignments

- Arithmetic operators

- Boolean equations

Dataflow is often the highest level that synthesis tools can handle

- Structural

- Boolean equations

- Hierarchy

- Physical Information

The structural representation is considered a netlist representation of the circuit

Ditched the rest of this and just did an example of using dataflow (case 1) and behavioral modeling (case 2) to demonstrate a 3-bit priority encoder for the microwave input circuit

### **Behavioral Modeling**

Think about circuits as implementing an algorithm (software = hardware)

- Process statement is the key: things within a process are implemented sequentially

- You can write a general algorithm within a process

- A process is executed continuously, but must have some sort of wait condition

- Until the wait condition is reached, you can think about all processes executing in the same delta-t.

- Within a process you can describe an algorithm

#### Designing combinational logic using asynchronous assignment statements

Say we want to implement our own XOR gate. In VHDL we just describe the function of the combination circuit just like we were writing a Boolean expression

#### Designing combinational circuits using a process statement

In a process statement we can write expressions like if statements, which makes coding some combinational logic easer.

```

entity FourToTwo is

port(inLines: in std_logic_vector(0 to 3); -- eight bits of input

outLines: out std_logic_vector(0 to 1); -- three output bits

```

```

inactive: out std_logic);

end eightToThree;

architecture behavioral of FourToTwo is

process(inLines) begin

if inLines(0) then

outLines <= "00";

inactive <= "0";</pre>

elsif inLines(1) then

outLines <= "01";</pre>

inactive <= "0':</pre>

elsif inLines(2) then

outLines <= "10";</pre>

inactive <= "0";</pre>

elsif inLines(3) then

outLines <= "11";</pre>

inactive <= "0";</pre>

else

outLines <= "000";</pre>

inactive <= "1";</pre>

end if;

end process;

end behavioral;

```

# **IEEE 1164 Data Types**

std\_ulogic

• Treat it like a bit, '0', '1' are what you will use most of the time

std\_logic

- Treat it like a bit, '0', '1' are what you will use most of the time

- Different is that std\_logic is "resolved", which means that there is a matrix that defines the output if two bits of type std\_logic are traveling over the same wire

std\_logic\_vector

- Vector of bits, need to declare it with the range of the indices and order left to right

- A: in std\_logic\_vector (2 downto 0);

- B: out std\_logic\_vector (0 to 7);

- Access by A(i) or B(i)

- Conceptually, the range labels the bits left to right

# **Combinational Logic Design Components**

Given a basic understanding of VHDL, we can now look at how we can represent MSI components as logic, netlist, dataflow, and behavioral elements.

MSI design components are functions that have prove to be useful in the design of digital circuits

• Basic building blocks for interface circuits, control logic, and medium complexity circuits

Read sections 5.1 and 5.2 on documentation and timing and follow them as appropriate

Aside: Rules for drawing MSI circuit elements

- Inputs on the left

- Outputs on the right

- Inputs that are inverse logic have a bubble (or overline)

- Outputs that are inverse logic have a bubble (or overline)

- Power connections are not normally shown

### Decoder

- Function

- Binary number as input

- One of  $2^n$  outputs is high

- With enable inputs, you can cascade decoders together to handle larger words

- Commercial binary decoders use negative logic on the output

- Logic diagram

- Each output has exactly one entry in the truth table

- Each output has a unique AND gate combination

- Enable is an additional input to each AND gate

- Netlist representation

- Entity and port statement

- component declarations in the declaration section of the architecture

- note: you have to write the definitions for inv and and3 as other VHDL files

- intermediate signal declarations

- port map statementes to instantiate each gate

```

library IEEE

use ieee.std_logic_1164.all

entity V2to4dec is

port ( I0, I1, EN; in std_logic;

Y0, Y1, Y2, Y3: out std_logic);

end V2to4dec;

architecture structural of V2to4dec is

signal invI0, invI0: std_logic;

component inv port(I: in std_logic; F: out std_logic);

end component;

component and3 port(a, b, c: in std_logic; F: out std_logic);

end component;

begin

U1: inv port map (I0, invI0);

U2: inv port map (I1, invI1);

U3: and3 port map (invI0, invI1, EN, Y0);

U4: and3 port map ( I0, invI1, EN, Y0);

U5: and3 port map (invI0, I1, EN, Y0);

U6: and3 port map ( I0,

I1, EN, YO);

end V2to4dec;

```

- Dataflow representation 1

- Use the concurrent with statement to determine the outputs

- Change the port statement to use a std\_logic\_vector on the inputs and outputs

- Note the use of **when others** to guarantee there are only 4 cases.

- Dataflow representation 2 (hierarchical)

- Say you want an easy way to control whether the output logic is active high or active low

- create a V2to4dec entity which uses active high logic (as above)

- Use a port map statement to insert it into an entity whose inputs or outputs are active low

- Control the logic level switching at the higher level.

- Behavioral style representation 1

- Use a process, with a case statement and an if statement

- Note the use of when others to limit the number of cases to 4

- Note the inclusion of Yi in the sensitivity arguments to the process statement

- The variables inside a process don't get their assignments until the process completes

- Therefore, it takes two passes through the process to get Yi assigned to Y, and we have to make sure and put Yi in the sensitivity list so that the process gets called twice

- Could make the if statement a concurrent conditional assignment and accomplish the same thing without having to include Yi in the process sensitivity list.

```

architecture behaviorall of V2to4dec is

signal Yi: std logic vector(0 to 3);

begin

process (EN, I, Yi) begin

case I is

when "00" => Yi <= "1000";

when "01" => Yi <= "0100";

when "10" => Yi <= "0010";

when others => Yi <= "0001";

end case

if EN = 1' then

Y <= Yi;

else

Y <= "0000";

end if;

end process;

end behavioral1;

```

# **Combinational Logic Elements**

Continue examination of how to design and work with MSI elements

### Decoder

Given the entity declaration:

```

entity V2to4dec is

port ( EN: in std_logic;

I: in std_logic_vector(0 to 1);

Y: out std_logic_vector(0 to 3));

end V2to4dec;

```

We can now complete our examination of the ways to represent the function

- Behavioral style representation 2

- Go all out and write an algorithm

```

Note that each bit is only written once within the process (Altera requirement)

•

architecture behavioral2 of V2to4dec is

begin

process (EN, I)

variable i: integer range 0 to 7;

А

begin

В

if EN = 1' then

for i in 0 to 7 loop

if i = conv_integer(A) then

Α

В

Y(i) <= `1';

else

Y(i) <= `0';

D

А

end if;

EN

В

end loop;

else

Y <= "0000";

A

end if;

В

end process;

end behavioral2;

```

What if we want a larger decoder?

- Cascade them using enable inputs

- If you have an N-output decoder, use the enable inputs to get a 2N-output decoder

- If you have an N-output decoder, use a 2-4 decoder to get a 4N-output decoder

### Encoder

- Function

- 2<sup>n</sup> inputs, any number of which may be high

- One binary number (n bits) as output, encoding the highest priority line that is high

- Most useful definition is behavioral

- Behavioral 1: use an if statement that expresses the priorities of the inputs

• Behavioral 2: use a for loop that loops through the inputs in order or priority

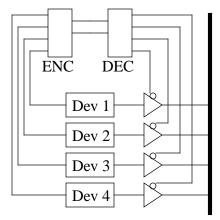

Note: with an encoder, decoder, and tri-state buffer we can start to make a bus and bus controller

- A bus is a set of wires that a number of devices may want to use

- Let the encoder handle all requests for the bus

- Send the output to a decoder that controls a set of tristate buffers

- The tri-state buffers control what goes on the bus

## Multiplexer (MUX)

- Function

- 2<sup>n</sup> input signals

- n input address

- enable signal

- 1 output, which is the signal indicated by the address

- Cool things you can do with a MUX

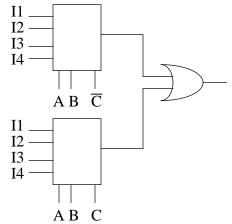

- Implement an arbitrary truth table for N variables

- Use it as an implementation of a ROM (identical to a truth table)

- Make big MUXs by cascading them using an enable inputs and putting the results through an OR gate

- Dataflow: Could have one conditional assignment statement (long)

- Behavioral 1: case statement is a multplexor

- It is generally implemented as such when synthesized to hardware

- This is why you want to make your case statements powers of 2, if possible

- Behavioral 2: convert the address to an integer and index into the input array to get the output

### Demultiplexer

- Function

- One input and one address as inputs

- 2<sup>n</sup> outputs, one of which gets the signal

- Same function can be executed with a decoder with an enable value

- Dataflow: one conditional case statement for each output

- Behavioral 1: case statement, one line for each address

- Behavioral 2: set all the outputs to 0, convert the address to an integer and set that output high

This is an alternative bus arrangement

- MUX controls what signal gets on the bus wire

- DEMUX controls where the signal goes at the other end

- Somehow have to decide who gets to send the signal and who gets to receive it

# **Combinational Logic Elements**

More complex combinational logic elements

### Comparators

An XNOR gate acts as a one-bit comparator: high if equal, low if not

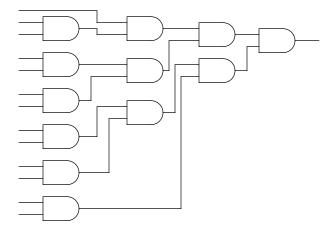

- To compare multiple bits, we could cascade XOR gates and AND gates (see below)

- This is the way Altera would implement a for loop: unfolding the logic

- A faster way is to compare multiple bits simultaneously and the OR the result

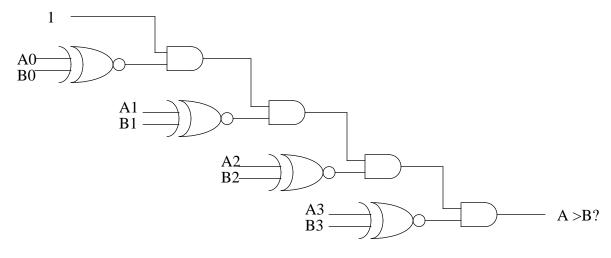

We could also do a cascade system to test for greater-than/less-than

- Greater-than: start with the MSB and work down

- Less-than: start with MSB and work down

- Real implementations use one AND gate for each case and then an OR gate to see if any of the potential greater than/less than situations are true

### Shifters/Rotators

We can use DEMUXs on the inputs to generate a shifter/rotator circuit (right shifter shown below)

- One DEMUX for each input

- Address of DEMUX indicates how much to shift the input

- Each output is an OR gate with inputs from the appropriate DEMUXs

## **Ripple Adders**

The first combinational circuit we looked at was an adder

- Can make a multiple-bit adder by cascading full-adders together

- Each adder takes A, B, Cin, and outputs S and Cout

- S = A XOR B XOR Cin

- Cout = AB + BCin + ACin

## **Carry Lookahead Adders**

Ripple-adders are slow: signal has to propagate

- Difficulty is the carry bit: use a circuit to precalculate the carry bits

- A particular full adder will generate a carry if its two addend bits are 1 (A,B)

- A particular full adder will propagate a carry if either of its two addend bits are 1

- At each level  $C_{i+1} = G_i + P_i * C_i$

- $G_i = X_i * Y_i$ : generate term

- $P_i = X_i + Y_i$ : propagate term

- We can iteratively expand this to get a two-level logic expression for the ith carry

- C1 = G0 + P0 \* C0

- C2 = G1 + P1 \* C1 = G1 + P1 \* G0 + P1 \* P0 \* C0

- C3 = G2 + P2 \* C2

- C3 = G2 + P2 \* (G1 + P1 \* G0 + P1 \* P0 \* C0)

- C3 = G2 + P2 \* G1 + P2 \* P1 \* G0 + P2 \* P1 \* P0 \* C0

- C4 = G3 + P3 \* C3

C4 = G3 + P3 \* (G2 + P2 \* G1 + P2 \* P1 \* G0 + P2 \* P1 \* P0 \* C0)

C4 = G3 + P3 \* G2 + P3 \* P2 \* G1 + P3 \* P2 \* P1 \* G0 + P3 \* P2 \* P1 \* P0 \* C0

- Each 4-bit adder circuit only takes 3 levels of logic to calculate the last carry

- Full binary adder is on pp. 437 of Wakerly

- Note the use of INVERT-OR-AND logic, which is the dual of AND-OR-INVERT

- This logic can be implemented in two layers of transistors, so it is as fast as one gate

- Carry equations are slightly different: Ci+1 = Pi \* Gi + Pi \* Ci

- Same equation, though, because Pi is always 1 if Gi is 1

- Allows factoring: Ci+1 = Pi \* (Gi + Ci) (this is source of the INVERT-OR-AND logic)

When you build large (i.e. 32-bit) adders, you use carry-lookahead between blocks as well as within a group

## ALUs

MSI Arithmetic Logic Units are all purpose computational circuits: see Wakerley pp. 439

- Shifting

- Rotating

- Bit-wise logical functions

- Subtraction

- Addition

ALUs generally have 8, 16, or 32 functions they can execute

• They will have carry in and carry out lines so that multiple ALU's can be cascaded to handle more bits of data

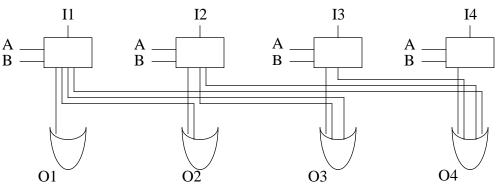

# **Programmable Logic Devices**

Circuits that use AND-OR combinations are common

• Can generate arbitrary truth tables using minterms

Programmable Logic Array: PLA

- N inputs and their inverses at the first level

- P AND gates with all possible inputs at the second level ( $P < 2^N$ )

- M OR gates with all possible inputs at the second level (M = number of outputs)

- The AND and OR gate levels both have fuses on all lines into each gate

- Blow the fuses to program the circuit

Programmable Array Logic: PAL

- OR-gate array is fixed (no fuses, fixed number of product terms)

- Outputs can be inputs of one block can be inputs to another block

- AND gates can connect to any input or the output of another block

- Output pins are bi-directional: one AND gate controls the direction of the pin

- Pin has a tri-state buffer at the output of the OR gate

- If the tri-state buffer is enable, the pin is an output

- Otherwise, it is an input since the OR gate does not connect to the wire

- Diagram on pp. 341 of Wakerly

Generic Array Logic: GAL

- EEPROM controls the fuses

- Output polarity can be controlled by an XOR gate on the output of each main OR gate

- fuse on the second input to the XOR gate which connects to ground

- if the fuse is blown, the XOR gate inverts the OR gate output

- Can be set up to do some sequntial logic as well by encoding a flip-flop out of NOR gates

Large Scale PLDs, of Complex PLD [CPLD]

- Altera MAX7000 family: thousands of logic gates in blocks, or macrocells

- The chip number indicates how many macrocells there are (e.g. 7128 has 128 cells)

- Electrically programmable

- Electrically erasable

- A "fitter" puts the designs on the chip

MAX 7000 family is built from a set of macrocells that each connect to I/O pins and to a programmable interconnect array [PIA].

- Each macrocell is a PAL device with an output flip-flop that can be used or bypassed

- A macrocell can send product terms to other macrocells, so that a single OR gate can have up to 20 product terms in it

- The output of the OR gate goes through an XOR gate so that the output can be inverted

There are several fixed inputs to a MAX7000 that are globally distributed

- Two clock inputs

- One reset input

## Field Programmable Gate Arrays [FPGA]

These are more complex, general programmable logic devices than CPLDs, and are designed so that state machines and arithmetic logic units are easy to configure.

FLEX10k family

- From 10,000 to 250,000 gate equivalents

- Consist of Logic Array Blocks [LAB] and Embedded Array Blocks [EAB]

- LABs consist of eight four-input lookup tables, each with a flip-flop on the output

- LABs are cascaded to they can be joined together to form full-adders, etc.

- EABs consist of 2048 bits of memory that can be configured in different ways

- EAB inputs and outputs can come from or go to a flip-flop

- All of the LABs and EABs are connected by row/column buses

- Each LAB/EAB can route information between its adjacent rows and columns

Xilinx XC4000 family

- From 2000 to 250,000 gate equivalents

- XC4000 is a 2-D array of configurable logic blocks [CLB]

- Each CLB contains 2 four-input lookup tables

- Each CLB has a flip-flop on the output

- Each CLB also has a 3-input LUT connected to the 2 four-input LUTs, which allows functions of 5 or more variables

- Each CLB can also serve as a 32x1 memory block (using both 4-input LUTs)

- CLBs are inteconnected using "routing channels"

- routing channels have different wires of various lengths

# **Sequential Logic**

•

Sequential logic circuits have memory

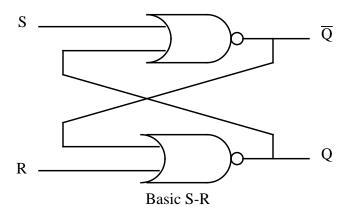

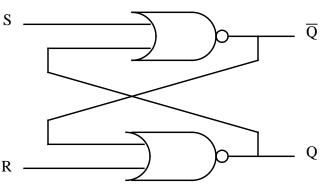

## Flip-flop: 2 NAND gates

What does this do?

- S-R Flip-flop

- Bistable device

- Give starting values to  $Q/\overline{Q}$

- Assign values to S/R

- Follow through the circuit

- S = 1: sets the flip-flop to 1

- R = 1: resets the flip-flop to 0

- S = R = 0: holds the flip-flop value

- S = R = 1: both outputs are 0, indeterminate value if S and R -> 0 simultaneously

# **Sequential Logic**

Sequential logic circuits have memory

#### Flip-flop: 2 NAND gates

What does this do?

- S-R Flip-flop •

- Bistable device

- Give starting values to  $Q/\overline{Q}$

- Assign values to S/R

- Follow through the circuit •

- S = 1: sets the flip-flop to 1 •

- R = 1: resets the flip-flop to 0 •

- S = R = 0: holds the flip-flop value •

- S = R = 1: both outputs are 0, inde-• terminate value if S and  $R \rightarrow 0$ simultaneously

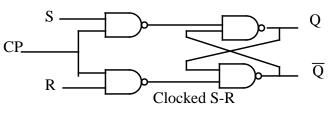

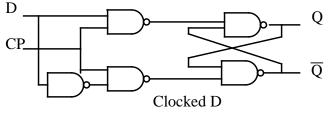

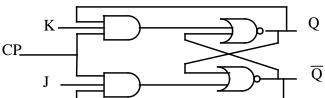

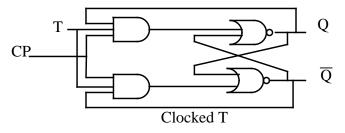

#### **Useful Flip-flops**

- Clocked S-R •

- D Flip-flop •

- JK Flip-flop ٠

- T Flip-flop •

Problem with basic flip-flops is that they can change as long as the clock is high

- Master-Slave Flip-flop •

- Two-flip-flops, with the clock • pulse inverted on the second

- Ouput only changes on the falling • edge

- D edge-triggered Flip-flop ٠

- pp. 215, [Mano 1991] •

- Also, pp. 543 [Wakerly, 2000]

- Output only changes on the rising edge

# **Sequential Logic**

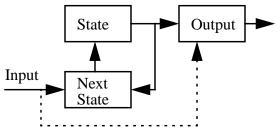

## **State Machines**

A sequential circuit can implement a state machine

- A state machine is a way of representing a time/history dependent process

- A state is a set of variables that represent all of the knowledge you need in order to predict the next state of the system given a set of inputs.

- State variables are held in flip-flops

- Next state calculation is a combinational circuit

- Feedback loop from the current state

- Also depends upon the current input

- Outputs are combinational circuits with at least the state variables as inputs

- Moore: output is only a function of the state variables

- Mealy: output is a function of both the state variables and the inputs

### **Designing a Sequential Circuit**

Define the task using words.

Determine, if possible from the task description, whether your outputs should be a function of only the state (Moore state machine), or a function of both the state and the inputs (Mealy state machine).

Draw a state diagram

- States are represented as circles

- Directed edges connect the states

- Inputs are list on the edges, as are outputs in a IN / OUT notation

- There should be one edge leaving each state for each possible input variable combination

Assign state values to the states

- Decide how many flip-flops are necessary (state variables)

- Decide how to assign values to the states

- binary

- gray codes

- based on output logic considerations

- based on similar meanings

- use all 0's or all 1's for the initial state (reset state)

Set up a state table

- Inputs

- State values

- Next state values

- Outputs

Minimize the number of states in the state table/diagram

- Two states are the same if

- They produce the same outputs for the same inputs •

- They go to the same next states (or equivalent next states) for all inputs •

Select a flip-flop type

- Based on your requirements

- Based on which one is easiest to use

- Based on which one optimizes the circuit •

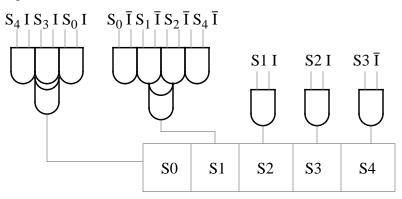

Design the combinational circuits

- For the flip-flop inputs

- For the output

Draw the logic diagram and build the circuit.

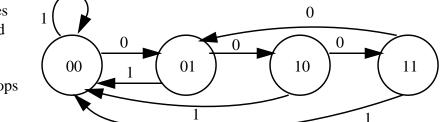

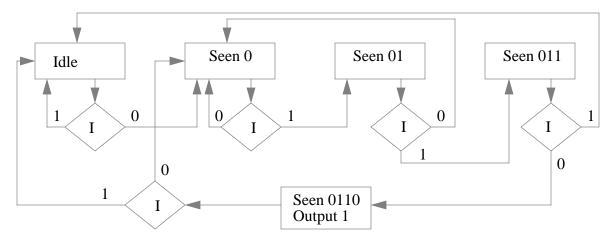

**Example:** 1.Design a state machine that holds a 1 value on the output for 1 clock cycle any time three 0's are received on a bit stream, with no overalap between sequences of 3.

- 1. Has to be a Moore machine to hold the output

- 2. Create the state diagram and assign values to the states 3. Create the state table and minimize the number of

- states (already done) 4. Select the kind of flip-flops to use: S-R.

| Input | A | В | A' | B' | Output | SA | R <sub>A</sub> | SB | R <sub>B</sub> |

|-------|---|---|----|----|--------|----|----------------|----|----------------|

| 0     | 0 | 0 | 0  | 1  | 0      | 0  | d              | 1  | 0              |

| 1     | 0 | 0 | 0  | 0  | 0      | 0  | d              | 0  | d              |

| 0     | 0 | 1 | 1  | 0  | 0      | 1  | 0              | 0  | 1              |

| 1     | 0 | 1 | 0  | 0  | 0      | 0  | d              | 0  | 1              |

| 0     | 1 | 0 | 1  | 1  | 1      | d  | 0              | 1  | 0              |

| 1     | 1 | 0 | 0  | 0  | 0      | 0  | 1              | 0  | d              |

| 0     | 1 | 1 | 0  | 1  | 0      | 0  | 1              | d  | 0              |

| 1     | 1 | 1 | 0  | 0  | 0      | 0  | 1              | 0  | 1              |

- 5. Calculate the logic equations for the output and flip-flop inputs

- The output is a function of only A and B •

- O = AB•

- The logic equations for the inputs to each flip-flop are functions of A, B, and I

- $S_A = \overline{I} \overrightarrow{A} B, R_A = IA + AB$   $S_B = \overline{I} \overline{B}, R_B = IB + \overline{A} B$

- 6. Build the circuit based on the logic equations

# **Sequential Logic**

## **Characteristic Excitation Tables**

Revisit the characteristic excitation tables

| Q | Q' | S | R | Q | Q' | D | Q | Q' | Т | Q | Q' | J | K |

|---|----|---|---|---|----|---|---|----|---|---|----|---|---|

| 0 | 0  | 0 | d | 0 | 0  | 0 | 0 | 0  | 0 | 0 | 0  | 0 | d |

| 0 | 1  | 1 | 0 | 0 | 1  | 1 | 0 | 1  | 1 | 0 | 1  | 1 | d |

| 1 | 0  | 0 | 1 | 1 | 0  | 0 | 1 | 0  | 1 | 1 | 0  | d | 1 |

| 1 | 1  | d | 0 | 1 | 1  | 1 | 1 | 1  | 0 | 1 | 1  | d | 0 |

Use these tables to fill in the flip-flop excitation values in the state transition table.

## **Example: Timer circuit**

Build a timer circuit that counts from 0 to 15 and outputs a high value on the 0, 10, and 14.

- 1. Has to be a Moore machine (only input is a clock)

- 2. State diagram is 16 states from 0 to 15, moving from one to the next.

- 3. Build state table: states cannot be minimized

| A | В | C | D | A' | B' | C' | D' | 0 | J <sub>A</sub> | K <sub>A</sub> | J <sub>B</sub> | K <sub>B</sub> | J <sub>C</sub> | K <sub>C</sub> | J <sub>D</sub> | K <sub>C</sub> |

|---|---|---|---|----|----|----|----|---|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| 0 | 0 | 0 | 0 | 0  | 0  | 0  | 1  | 1 | 0              | d              | 0              | d              | 0              | d              | 1              | d              |

| 0 | 0 | 0 | 1 | 0  | 0  | 1  | 0  | 0 | 0              | d              | 0              | d              | 1              | d              | d              | 1              |

| 0 | 0 | 1 | 0 | 0  | 0  | 1  | 1  | 0 | 0              | d              | 0              | d              | d              | 0              | 1              | d              |

| 0 | 0 | 1 | 1 | 0  | 1  | 0  | 0  | 0 | 0              | d              | 1              | d              | d              | 1              | d              | 1              |

| 0 | 1 | 0 | 0 | 0  | 1  | 0  | 1  | 0 | 0              | d              | d              | 0              | 0              | d              | 1              | d              |

| 0 | 1 | 0 | 1 | 0  | 1  | 1  | 0  | 0 | 0              | d              | d              | 0              | 1              | d              | d              | 1              |

| 0 | 1 | 1 | 0 | 0  | 1  | 1  | 1  | 0 | 0              | d              | d              | 0              | d              | 0              | 1              | d              |

| 0 | 1 | 1 | 1 | 1  | 0  | 0  | 0  | 0 | 1              | d              | d              | 1              | d              | 1              | d              | 1              |

| 1 | 0 | 0 | 0 | 1  | 0  | 0  | 1  | 0 | d              | 0              | 0              | d              | 0              | d              | 1              | d              |

| 1 | 0 | 0 | 1 | 1  | 0  | 1  | 0  | 0 | d              | 0              | 0              | d              | 1              | d              | d              | 1              |

| 1 | 0 | 1 | 0 | 1  | 0  | 1  | 1  | 1 | d              | 0              | 0              | d              | d              | 0              | 1              | d              |

| 1 | 0 | 1 | 1 | 1  | 1  | 0  | 0  | 0 | d              | 0              | 1              | d              | d              | 1              | d              | 1              |

| 1 | 1 | 0 | 0 | 1  | 1  | 0  | 1  | 0 | d              | 0              | d              | 0              | 0              | d              | 1              | d              |

| 1 | 1 | 0 | 1 | 1  | 1  | 1  | 0  | 0 | d              | 0              | d              | 0              | 1              | d              | d              | 1              |

| 1 | 1 | 1 | 0 | 1  | 1  | 1  | 1  | 1 | d              | 0              | d              | 0              | d              | 0              | 1              | d              |

| 1 | 1 | 1 | 1 | 0  | 0  | 0  | 0  | 0 | d              | 1              | d              | 1              | d              | 1              | d              | 1              |

- 4. Select J-K flip-flops for this circuit.

- 5. Calculate the logic equations:

- $J_{D} = K_{D} = 1$

- $J_{C} = D, K_{C} = D$

- $J_B = CD, K_B = CD$

- $J_A = BCD, K_A = BCD$

- $\overline{O} = \overline{A} \overline{B} \overline{C} \overline{D} + A C \overline{D}$

- 6. Build the circuit

# **Useful Sequential Circuits**

# **Simple Registers**

A set of D flip-flops with the load line being the clock pulse

Need logic attached to the clock pulse to enable/disable the load feature of the register

- Usually a system will have a master clock

- We want delays in clock to be minmal at best •

- Logic between the clock and the flip-flop inputs delay the system

SR flip-flop register with parallel load and clear

- Load signal goes through a buffer •

- Reduce the fan-out seen by other circuits

- Inputs to SR go through AND gates with the load signal

- Clear signal goes directly to the FF clear input

- Register clock goes through an inverter to decrease the load on the master clock

- Flip-flops change state on the falling edge of the master clock

D flip-flop register with parallel load and clear

- When load line is high, the inputs are ANDed with the load line to drive the D inputs

- When the load line is low, the D outputs are ANDed with the inverse load line to drive the D inputs

- D flip-flop value must be fed back around in order to maintain its value when the load line is low because there is no way to tell a D flip-flop to maintain its last value

# **Example: ROM and a Register**

If we have a large truth table, we may want to implement the circuit with ROM and a register.

- 2<sup>N</sup> states

- Given a truth table with I inputs, N state variables, N next state values, and M outputs

Create an N + I input ROM (2<sup>N+I</sup> words) with N + M outputs

- Feed N of the output values back into the register at each clock cycle

- Outputs come directly from the ROM

- 2-chip circuit implementation of a very complex state machine •

- simple uCode controller for a processor

# **Useful Sequential Circuits**

## **Shift Register**

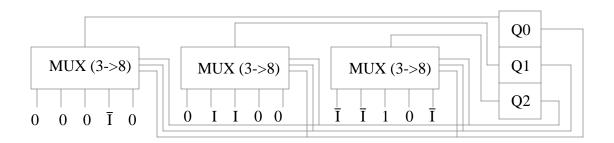

Bi-directional shift register with parallel load

- Register can shift the values left one bit, right one bit, load in parallel, and maintain

- Register also has a parallel clear input

- You can implement one using D flip-flops and a MUX for each bit.

- 1. Clear control to clear the register to 0

- 2. CP input for a clock pulse

- 3. Control lines: 00 =maintain, 01 =load input, 10 =shift left, 11 =shift right

- 4. N input lines, as well as left and right input lines

Use MUXs on the D flip-flop input and have 2 input select lines:

- Clear is buffered

- Clock is inverted

# Counters

A counter is a register with an incrementer circut on each bit: half-adder

- It's like adding 0 to the current value with a carry-in

- An XOR gate handles the new value of each bit

- An AND gate handles the carry propagation

- You can do carry-lookahead to speed things up

To make an up-down counter you use a half-adder subtractor

- Add a direction input D: 0 = count up, 1 = count down

- Add an enable input E: 0 = don't change, 1 = follow direction input

- New bit value is still an XOR gate for both directions

- New carry value is  $C_{i+1} = \overline{D}Q_iC_i + D\overline{Q}_iC_i$

- Enable input is the C<sub>0</sub> input

To make a presetable up-down counter you use:

- HAS for each bit

- load inputs

- a 2-1 MUX to handle the loading v. counting

## BCD counters

- Set up circuitry so that instead of counting to 10, it loads 0 after reaching 9

- To effect an up-down BCD counter, you want to load either 0 or 9 upon reaching 9 or 0.

- Use a 2-1 selector for each bit of the load inputs to load either 0 or 9.

- Have the load go high when the outputs are either 0 or 9 in the appropriate direction

- Have the direction input specify whether to load the 0 or 9 at the next clock

- This requires a synchronous load in order to work!

- With asynchronous load you have to do other things

- AND the clock and a 10 output together and feed it into the load signal for counting up

- AND the clock and a 15 output together and feed it into the load signal for going down

Ripple counters

- You can make a very simple counter using T flip-flops

- Connect the inverse output of each bit to the clock of the next bit

- Have an enable line go in parallel to each T input (1 = enabled, 0 = hold)

- Connect the clock to the first bit

- Ripple counters are slow, but easy to build

- You can make faster ripple counters by using blocks of 4 bits and calculating the carry between chips

#### **Timing signals**

You can use a counter as a timer

- Select a flip flop of the timer as an output to divide the clock frequency by a power of 2

- On a synchronous counter ('163), set it up so that when it reaches a certain value it resets or loads a new value on the next rising edge.

Ring counter

- A set of flip-flops where a 1 goes around in a circle

- $2^{N}$  stage pulse timer

- N-bit counter connected to a decoder to create 2<sup>N</sup> staggered timing signals

- Commonly used in computer systems to control different stages of operation

Duty cycle

- The duty cycle of a timer is the percentage of time it is at a high voltage

- 50% duty cycle is equal time on and off

- 25% duty cycle means a pulse of duration 1 within a period of duration 4

#### **Example: Serial to Parallel Converter**

Build a circuit that takes a clock and a bit stream as input. In the idle state, the bit stream input is low, and the circuit waits for input. Upon receiving a high bit, the circuit then collects the next eight bits (data) into a register and an optional ninth bit (parity) depending upon a parity flag. The clock signal after receiving the last bit (8th or 9th), the circuit should output a high signal indicating data is ready.

# **Useful Sequential Circuits**

## **Timing signals**

You can use a counter as a timer

- Select a flip flop of the timer as an output to divide the clock frequency by a power of 2

- On a synchronous counter ('163), set it up so that when it reaches a certain value it resets or loads a new value on the next rising edge.

Ring counter

• A set of flip-flops where a 1 goes around in a circle

2<sup>N</sup> stage pulse timer

- N-bit counter connected to a decoder to create 2<sup>N</sup> staggered timing signals

- Commonly used in computer systems to control different stages of operation

Duty cycle

- The duty cycle of a timer is the percentage of time it is at a high voltage

- 50% duty cycle is equal time on and off

- 25% duty cycle means a pulse of duration 1 within a period of duration 4

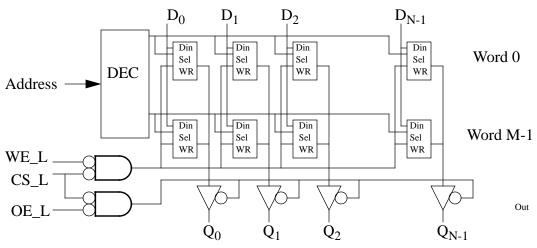

# **Register Files**

For fast access of a small number of registers (cache, register files in a CPU)

- 2D array of flip-flops that each have the following inputs

- read enable

- write enable

- input

- clock

- $D = WE * Input + \overline{WE} * Q$

- Output is a 3-state buffer with output enable = read enable line

- Register files can often read two registers per cycle and write to two registers per cycle

- Decoders determine which register (row) to read/write, with one decoder for each operation.

# RAM

## Static (SRAM)

- Information stored in flip-flops

- Faster

- Valid as long as the power is on

- Takes more chip space per bit (at least 2 NAND gates (8 transistors) per bit)

- Typically used for registers and cache

# Dynamic (DRAM)

• Information stored in capacitors

- Slower

- Charge dissapates every few milliseconds

- Takes less chip space per chip (one transistor per bit)

- Typically used for main memory on computer systems

#### RAM read/write process

- 1. Chip select

- 2. Decode the address

- 3. Activate the appropriate locations in memory

- 4. Write data to the memory cells / Interpret and output data

With each bit you need to be able to get:

- Input

- Output

- Read/write

- Select

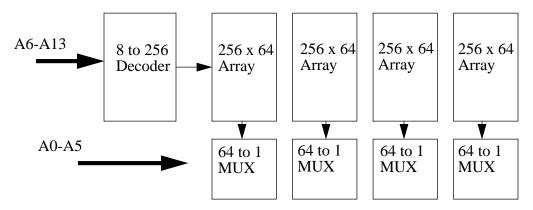

Like in the ROM, a decoder selects the word (N inputs, 2<sup>N</sup> output lines)

We also need to be concerned about timing

- Address decoding takes time

- Chip selection takes time

- RW select takes time

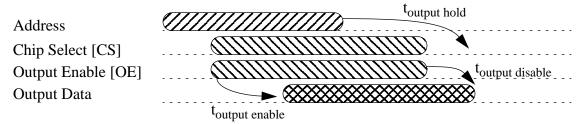

Timing pattern for reading: governed by CS and OE inputs

- Put address on the address lines

- Set chip select [CS] and output enable [OE]

- Output enable time determines when the data is ready to be read

- Address can be changed without affecting the output for a certain amount of time

output hold time

- Chip deselect

- Outputs are still good for a certain amount of time

- output disable time

| Address            | Coutput hold                     |

|--------------------|----------------------------------|

| Chip Select [CS]   |                                  |

| Output Enable [OE] | allillillillilli toutput disable |

| Output Data        |                                  |

|                    | t <sub>output</sub> enable       |

# RAM

Timing pattern for reading: governed by CS and OE inputs

- Put address on the address lines

- Set chip select [CS] and output enable [OE]

- Output enable time determines when the data is ready to be read

- Address can be changed without affecting the output for a certain amount of time

- output hold time

- Chip deselect

- Outputs are still good for a certain amount of time

- output disable time

Timing parameters for read operations

- t<sub>AA</sub>: Access time from address. This is how long it takes for the data to be valid given a new address on the address lines (and assuming CS and OE are enabled)

- $t_{ACS}$ : Access time from chip select, assuming OE and address. This is usually the same as  $t_{AA}$ , but not always (enables the decoder signal)