| A D-Latch in VH<br>entity mydlatch is port (<br>signal d, gate: in std_logic;<br>signal q: out std_logic<br>);<br>end mydlatch;<br>architecture behavior of mydlatch is<br>rising edge triggered DFF | DL                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| state: process (gate)<br>if (gate = '1') then<br>q < = d;<br>end if,<br>end process;<br>end behavior;                                                                                                | No default<br>assignment for<br>'q'; only assigned<br>when gate is high. |

| BR 8/99                                                                                                                                                                                              |                                                                          |

BR 8/99

BR 8/99

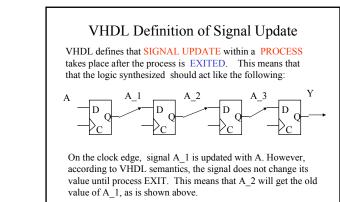

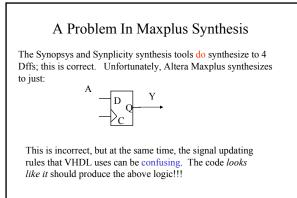

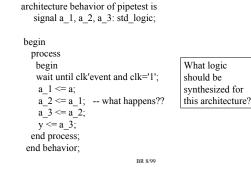

## A Problem with VHDL Semantics vs Maxplus Synthesis.....

BR 8/99

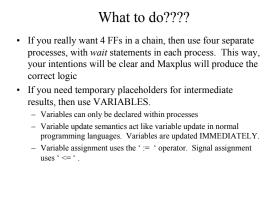

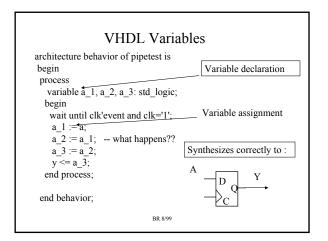

## Variables vs. Signals ALWAYS use variables for temporary values within processes However, for the RTL done in this class I doubt if you will ever need to use variables. Use SIGNALS for passing information between

- processes - Variables cannot be used outside of processes

- A variable 'x' in a process cannot be accessed by other processes. Can only be used within the process it is declared

BR 8/99

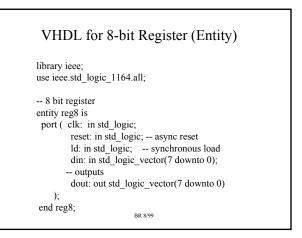

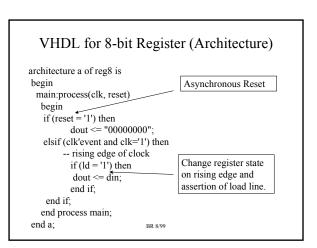

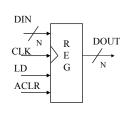

## Registers

The most common sequential building block is the register. A register is N bits wide, and has a load line for loading in a new value into the register.

Register contents do not change unless LD = 1 on active edge of clock.

A DFF is NOT a register! DFF contents change every clock edge.

ACLR used to asynchronously clear the register

BR 8/99