## Verilog RTL Modeling

- · This assignment introduces you to Verilog RTL modeling

- · Similar in concept to VHDL RTL, just different syntax

- · Will use serial data transfer as the problem to be solved

11/6/2002 BR 1

## Serial Communication

- Serial communication is as widely (or even more widely used) than parallel communication

- Especially true if communication occurs over long wires

- Many new high speed serial communication standards have been developed

- USB, IEEE Firewire, HyperTransport, etc.

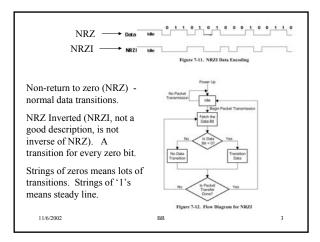

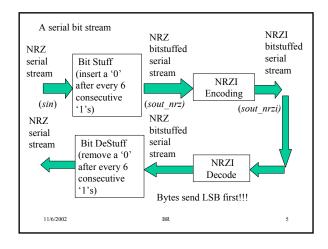

- This lab will introduce you to some basic serial communication concepts, namely bit-stuffing and NRZI encoding

- These techniques are used in the USB (Universal Serial Bus) interface.

11/6/2002 BR 2

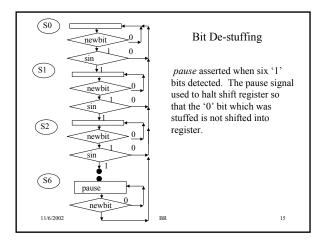

Bit Stuffing – a '0' is inserted after every six consecutive '1's in order to ensure a signal transition so that receiver clock can remain synchronized to the bit stream.

Data Encoding Sequence:

Raw Data

Sync Pattern

Packet Data

Sync Pattern

Packet Data

Figure 7-13. Bit Stuffing

Bit stuffing done automatically by sending logic. Sync pattern starts data transmission and is seven '0's followed by a '1'.

### The Task

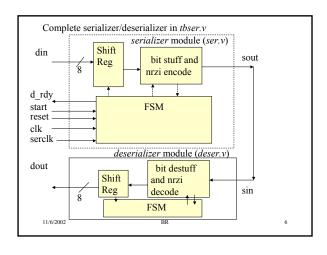

- You are to design the serializer module (in file ser.v) using Verilog RTL

- May need several modules within file ser.v, top level module is called serializer and has the interface shown

- Your ser.v code must be synthesizeable

- I have designed *deserializer* module (in file *deser.v*) and testbench (*tbser.v*).

- Testbench connects the serializer/deserializer modules together

- Also sends 32 bytes to serializer/deserializer for testing purposes

11/6/2002 BR

## Serializer Module

- · Should wait until start is asserted

- · Send value on din serially over sout

- · Request new value on din by asserting d rdy

- In testbench, there is a clock cycle latency between assertion of d rdy and a new din value being provided

- · Continually send serial data until reset is asserted.

- Main clock is signal clk. The serial clock is serclk which has 1 clock pulse for every 4 pulses on clk.

- New serial data should be provided for every pulse on serclk.

- Both clk and serclk provided by testbench.

11/6/2002 BR 8

# Zip Archive serial.zip

- Contains directory serial, which contains files tbser.v, ser.v, deser.v.

- Also contains a Modelsim golden waveform called serial\_vsim.wlf and command file serial\_wave.do To view this waveform do:

- qhsim-view serial vsim.wlf-do "do serial wave.do"

- Shows all signals in tbser.v from golden simulation.

- · The file qhsim gold log.txt contains the golden output

- Testbench just sends 32 bytes to serializer/deserializer

- Each time a new byte comes out of the deserializer, it is printed to screen.

- Synopsys script file ser.script for testing if verilog code is synthesizeable.

11/6/2002 BR 9

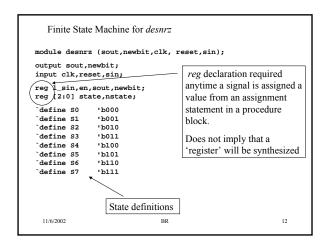

```

Procedural block for FSM state storage

Triggered on rising edge of

clock, so outputs will have

always @(posedge clk) begin

a rising-edge DFF

if (reset == 1),

begin

synthesized.

state = `SO;

l_sin = 1;

sout = 1;

Synchronous reset

end

else state = nstate;

en asserted by FSM

newbit = 0;

if (en == 1) begin

logic every 4 clocks

if (1_sin !== sin) sout = 0;

else sout = 1;

since we know serial

clock is 1/4 clock freq.

newbit = 1;

l_sin = sin;

end

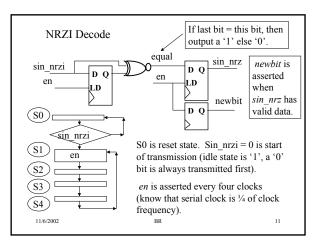

l sin is last serial input. If last serial input not equal

end

to current serial input, then was a '0' value. If the last

serial bit is equal to current bit, then a '1'. The newbit

asserted to indicate a valid serial output bit.

11/6/2002

BR

```

```

Combinational Block

Triggered on any changes to

state or sin

always @(state or sin) begin

nstate = state; 🕳

Default output assignments

en = 0:

(en negated, stay in same

case (state)

state)

SO: // wait for start edge

if (sin == 0) nstate =

`s1;

`S1: begin 🔨

en = 1; nstate = `S2;

end 👡

`S2: nstate = `S3;

Need begin/end if more

`S3: nstate = `S4;

than one statement in

S4: nstate = `S1;

block.

default: nstate = `SO;

endcase

end

endmodule

11/6/2002

BR

14

```

```

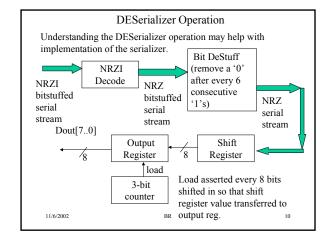

8-bit Shift register in deser.v

module des_shift (dout, sin, clk, reset, newbit,pause);

output [7:0] dout;

input clk, reset, newbit, pause, sin;

reg [7:0] dout;

always @(posedge clk) begin

if ((newbit == 1) && (pause == 0)) begin

dout = dout >> 1; ←

Shift occurs if newbit

dout[7] = sin;

available and not

if (reset == 1) dout = 'b00000000' destuffing (pause == 0).

end

endmodule

Data sent LSB first so shift data

into MSB.

Synchronous reset

11/6/2002

BR

16

```

```

3-bit Counter register in deser.v

module descnt (dout, zero, clk, reset, newbit, pause);

output [2:0] dout;

output zero;

input clk, reset, newbit, pause;

reg [2:0] dout;

Assert zero when counter

reg zero;

value = 0. This output used

always @(dout) begin

to control loading of output

if (dout == 'b000) zero = 1;

else zero = 0;

register.

end

always @(posedge clk) begin

if ((newbit == 1) && (pause == 0)) dout = dout + 1;

if (reset == 1) dout = 'b000;

end

Increment counter if newbit available

endmodule

and not destuffing.

11/6/2002

BR

17

```

```

8-bit Register in deser.v

module outreg (q,d,r,clk,ld);

output [7:0] q;

input [7:0] d;

input r,clk,ld;

req [7:01 q;

Hex formatting

always @(posedge clk) begin

if (ld == 1) q = d;

if (r == 1) q = 'h00;

end

endmodule

Note that synchronous reset takes

precedence over synchronous load.

11/6/2002

BR

18

```

```

Deserializer module - connects other modules together

module deserializer (dout, clk, reset, sin);

output [7:0] dout;

input clk, reset, sin;

Must explicitly declare the

wire [2:0] bitcnt;

widths of any wires whose

wire [7:0] sdout;

width is not 1. (default

wire [7:0] dout;

width is 1).

dff u_dff (lat_sin,sin,reset,clk);

desnrz u_desnrz (sout_nrz,newbit, clk, reset,lat_sin);

destuff u_destuff (sout,pause,newbit,sout_nrz,reset,clk);

descnt u_descnt (bitcnt, zero, clk, reset, newbit,pause);

des_shift u_shift (sdout, sout, clk, reset, newbit,pause);

outreg u_outreg (dout,sdout,reset,clk,zero);

endmodule

11/6/2002

BR

19

```

```

Continual Assignment vs. Procedural assignment

reg zero;

always @(dout) begin

if (dout == 'b000') zero = 1;

else zero = 0;

end

Can also be done as shown below. This style is known as a continuous assignment. Only used for combinational logic blocks. Output (right hand side) updated anytime an event occurs on any signal in left hand side.

assign zero = ~dout[2] & ~dout[1] & ~dout[0];

11/62002

BR 20

```

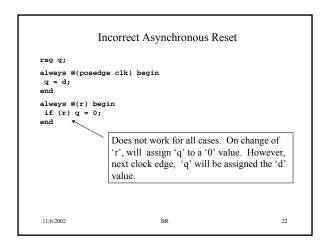

```

Asynchronous vs Synchronous Inputs

Synchronous reset

always @(posedge clk) begin-

if (r == 1) q = 0; *

else q = d;

reg q;

Asynchronous reset -

always @(posedge clk) begin

note use of

q = d;

assign/deassign in

end

always @(r) begin

procedure block.

if (r) assign q = 0;

'desasign' needed to

else deassign q;

disable continuous

end

drive when reset = 0

11/6/2002

BR

```

```

tbser module in tbser.v

module tbser;

reg clk, reset, start;

Declaration of wires

wire [7:0] din;

with non-default widths

wire [4:0] addr;

wire [7:0] dout;

reg [7:0] last_dout;

Any block with 'initial'

initial begin

clk = 0;

keyword only executed

reset = 1;

once.

start = 0;

last_dout = 'h00;

end

BR

23

11/6/2002

```

# tbser module in tbser.v cont. trace block prints dout value anytime it changes and serclk is asserted. Can name blocks (not required) if (serclk == 1) begin if (last\_dout !== dout) \$display("Dout = %h ",dout); end end Print in hex format.

### tbser module in tbser.v cont. always begin : stim stim block provide stimulus for @(posedge clk); @(posedge clk); reset = 0; input signals. @(posedge clk); Note use of @(posedge clk) -start = 1; @(posedge clk); waits until rising edge before continuing. start = 0; while (addr == 0) begin @(posedge clk); end while (addr !== 0) begin @(posedge clk); end while (addr == 0) begin @(posedge clk); end \$finish; end 11/6/2002 BR 26